Signal clock_div : STD_LOGIC_VECTOR(4 downto 0) On the home built CPLD board, the LEDs will all initially be switched on because of the wiring of the LEDs to the CPLD which effectively inverts the logic level on the CPLD pin.Īrchitecture Behavioral of shift_register_top is

#Parallel input serial output shift register vhdl code code

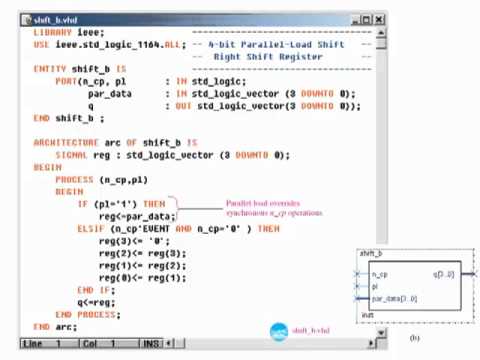

The shift_reg register is 8 bits wide and the VHDL code connects each bit in the register to an LED, so that 8 LEDs show the value in each bit of the register. This register is initialized with the value of 00h so that when power is switched on to the CPLD board, the register will be cleared. This example creates a shift register using a VHDL signal called shift_reg shown in the code listing below. These shift registers are both serial to parallel shift registers as they take the serial data from the D input and shift it for display on 8 LEDs in parallel.īooks that may interest you: First Shift Register Both VHDL code examples of the shift register behave in exactly the same way when implemented on the CPLD. This video shows the VHDL shift register in action. The two different examples create the same shift register using slightly different VHDL code. There are two examples of a shift register written in VHDL below. It is also possible to shift data from right to left and to use the LSB as an input for serial data. The Shift Register as Created in VHDL Code Data is shifted from left to right – from Most Significant Bit (MSB) to Least Significant Bit (LSB). The image below shows an eight bit shift register that is created in VHDL code in this tutorial. The data in each flip-flop will be shifted to the flip-flop on its right when the rising edge of the clock pulse occurs.Ī Shift Register is Made from D-type Flip-flops Whatever the state of the data input when the rising edge of the clock pulse occurs will be the logic level that is shifted into the first flip-flop. This data can be either a 0 or a 1 and will be shifted to the right on each rising edge of the clock pulse. This shift register is configured to shift data from the left to the right.ĭata is fed into the D input of the first flip-flop on the left. This is a four bit shift register and therefore consists of four D flip-flops.

Shift registers consist of D flip-flops as shown in the figure below. A shift register has the capability of shifting the data stored in the register from left to right or right to left. Shift Register OperationĪ register stores data i.e. Two different ways to code a shift register in VHDL are shown. A shift register is written in VHDL and implemented on a Xilinx CPLD.

0 kommentar(er)

0 kommentar(er)